Main Memory #2 페이징과 스와핑

1. 페이징(paging)

페이징의 필요성

프로세스를 메모리에 올릴떄 가장 좋은 시나리오는 메모리에서 연속적인 위치에 그대로 올라가는 것이다. 하지만 프로세스의 크기가 커지면 커질 수록 연속적인 위치에 놓지 못하게 됨. 이렇게 되면 메모리 위에서 프로세스는 쪼개지는 외부 단편화가 발생

페이징이란 무엇인가?

- 프로세스의 물리적 주소 공간을 비연속적으로 허용하는 메모리 관리 체계이다

- 연속적인 메모리 할당의 2가지 문제를 극복한다

- 외부 단편화(External fragmentation) 회피

- 압축과 관련된 요구를 회피

- 운영체제와 하드웨어 사이에서 협력하여 구현

페이징의 기본적인 방법

- 물리적인 메모리를 고정된 크기의 블록(Frames)으로 분할

- 논리적인 메모리를 같은 크기의 블록(pages)dmfh qnsgkf

ex) 메모리의 크기가 1GB 크기라고 가정. 그리고 물리적인 메모리를 1KB단위로 분할하여 Frames 으로 만든다면 1GB = 1024KB * 1024 = 1,048,576KB이므로 대략 100만개의 frames 블록이 생성된다. 그리고 프로세스의 크기는 64KB라고 가정한다. 이렇게 되면 프로세스는 64개의 frames가 있게 된다 그런다음 64개의 frames를 물리적 메모리에 올리게 된다. 여기서 주목할 점은 64개의 frames로 분할했기 때문에 메모리위에서 연속적일 필요는 없다.

- CPU에 의해서 생성된 모든 주소는 2가지 부분으로 나뉨

- 페이지 번호(page number, p)

- 페이지 오프셋(Page offset, d)

페이지 번호

- 페이지 번호는 프로세스마다 페이지 테이블에 대한 인덱스로 사용됨

- 논리적인 주소의 페이지 번호는 물이적인 주소의 플임 번호로 매핑됨

- 논리적인 주소의 페이지 오프셋을 프레임의 시작 위치에 더하야 접근

논리적 주소를 물리적 주소로 변환하기 위한 단계

- 페이지 번호 p를 추출한 다음 페이지 번호 p는 페이지 테이블의 인덱스로써 사용

- 페이지 테이블로 부터 페이지 번호 p에 따른 프레임번호 f를 추출

- 페이지 번호를 p를 프레임 번호 f로 변경

- page 0번의 인덱스는 0으로써 page table의 0번 인덱스를 찾아간다.

- page 0의 프레임 번호는 1번으로써 물리적인 메모리의 프레임 1번에 올린다.

페이지 크기(page size)

- 페이지의 크기는 하드웨어에 의해서 정의됨

- 논리적 주소 공간의 크기가 2^m이고 페이지의 크기가 2^n이라면 페이지 번호의 최대 필요 bit수와 페이지 오프셋의 최소 필요 bit수는 다음과 같습니다

- 페이지 번호의 최대 필요수 bit: m-n bit

- 페이지 오프셋의 최소 필요수 bit 수 : n bit

- 예를 들어 m =10이라면 논리적 주소 공간은 2^10dlrh n=2라면 페이지의 총크기는 4이다.

- 페이지 번호는 8bit로 표현하고 페이지 오프셋은 2bit로 표현한다

4byte 크기의 페이지를 가진 16byte 크기를 가진 논리적인 주소를 이용하여 페이지 테이블에 매핑하여 물리적인 주소 공간에 올리는 그림입니다. n = 2^2 = 4, m = 2^4 = 16이 됩니다.

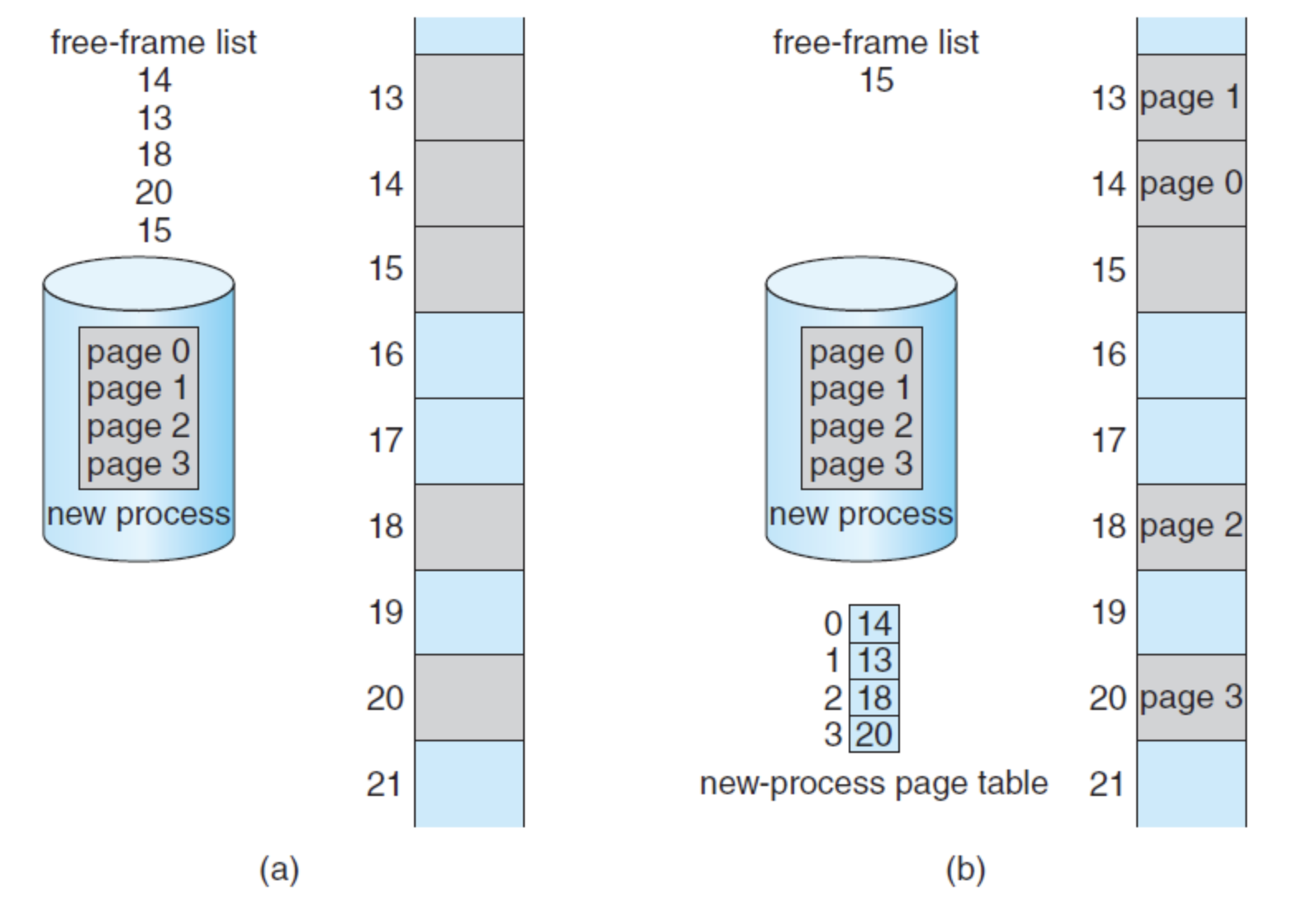

실행할 시스템에 프로세스가 도착한 경우

실행할 시스템에 프로세스가 도착한 경우에 메모리 할당을 위해 페이지로 표현된 크기가 검사됩니다. 페이지들을 비어있는 프레임 리스트에 매핑시켜 메모리에 할당한다. 그결과 비어있는 프레임은 15번 밖에 안남음

하드웨어의 지원

- CPU 스케줄러가 실행을 위해서 프로세스를 선택할때 페이지 테이블을 문맥교환Context switch 하는동안 다시 불러와야합니다. 왜냐하면 그 페이지 테이블이 계속 유지될거라는 보장이 없기 때문

- 그래서 페이지 테이블을 가르키는 포인터는 각각의 프로세스의 PCB에 다른 레지스터 값들과 같이 저장되어야한다. 페이지 테이블 포인터를 사용하는 이유는 프로세스가 커지면 커질수록 페이지 테이블 자체를 다시 불러오는 것이 비용이 많이 들기 때문. 그래서 이문제를 해결하기 위해서 PTBR(page-table base register)를 이용

PTBR(Page-Table Base Register)

- PTBR은 페이지 테이블의 시작 위치를 가리키는 포인터

- 페이지 테이블 자체는 메인 메모리에서 유지

- 프로세스간의 문맥 교환할때 빠르지만 메모리 접근 시간은 느림

- 메모리 접근이 2번 필요하다는 단점이 있음

- 페이지 테이블 엔트리를 위해서 한번

- 실제 데이터(프레임 블록)를 위해서 한번

Translation Look-aside Buffer(TLB)

- TLB는 페이지 테이블의 캐시 역할을 수행

- 하드웨어인 캐시메모리 사용

TLB를 사용한 효율적인 메모리 접근 시간

- TLB hit : 만약 TLB안에 찾고자 하는 페이지 번호가 있는 경우 TLB hit라고 표현합니다.

- TLB miss : 만약 TLB안에 찾고자 하는 페이지 번호가 없는 경우 TLB miss라고 표현합니다.

- hit ratio : TBL에서 찾고자 하는 페이지 번호를 찾은 횟수 비율

- 예를 들어 어떤 시스템의 메모리에 접근하는 10나노초 걸린다고 가정합니다. TLB를 거치지 않고 페이지 테이블을 거치는 시간은 20나노초 걸린다고 가정합니다. hit ratio에 따른 접근 시간은 다음과 같습니다.

- 80% hit ratio : EAT = 0.80 * 10 + 0.20 * 20 = 12ns.

- 99% hit ratio : EAT = 0.99 * 10 + 0.01 * 20 = 10.1ns.

,,,,,,

'Etc' 카테고리의 다른 글

| [운영체제]chapter 09. Main Memory_#01 주 메모리의 관리 (1) | 2024.06.13 |

|---|---|

| [운영체제]chapter 08. Deadlock_#03 교착상태 탐색 후 회복 (1) | 2024.06.13 |

| [운영체제]chapter 08. Deadlock_#02 교착상태와 뱅커 알고리즘 : 교착상태 회피 (0) | 2024.06.12 |

| [운영체제]chapter 10. Vurtual Memory_#02 (0) | 2024.06.12 |

| [운영체제]chapter 10. Vurtual Memory_#01 (0) | 2024.06.11 |